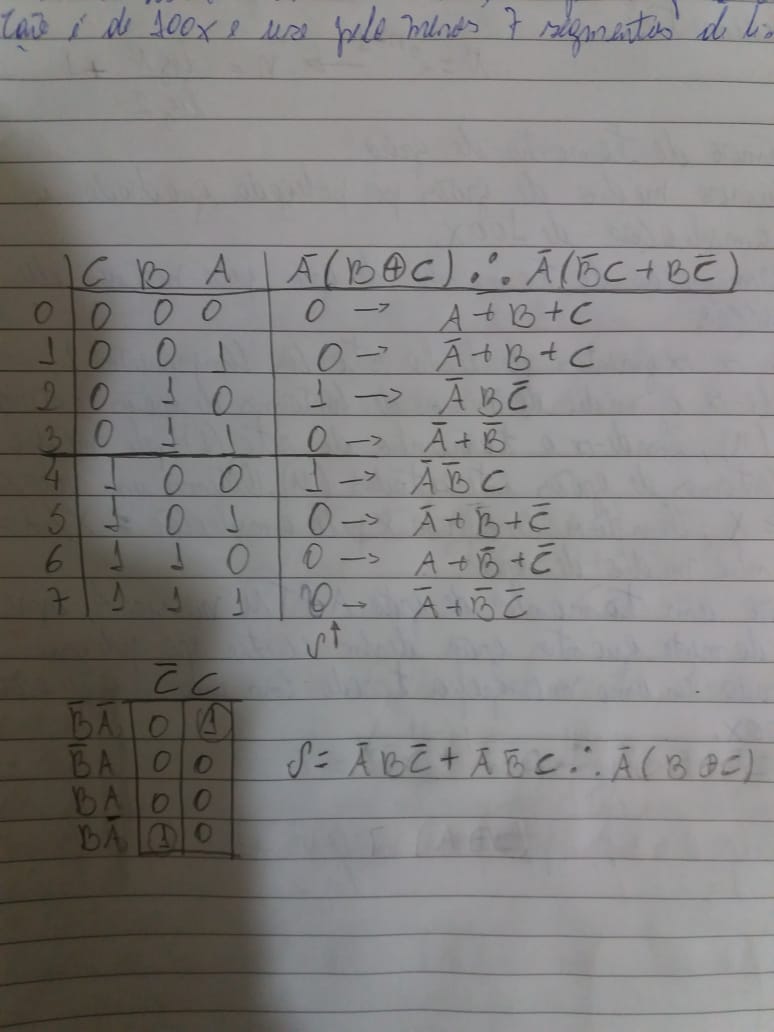

Utilize o Mapa de Karnaugh para representar a seguinte expressão booleana na forma de soma e produtos: S= Ā (B⊕c)

Alguem poderia me responder??

💡 3 Respostas

Paulo Henrique

Era essa a resposta que voce queria??

RD Resoluções

Maurice Karnaugh, engenheiro de telecomunicações, desenvolveu o mapa de Karnaugh no Bell Labs em 1953 enquanto projetava circuitos baseados em lógica digital. Agora que desenvolvemos o mapa de Karnaugh com a ajuda dos diagramas de Venn, vamos colocá-lo em uso. Os mapas de Karnaugh reduzem as funções lógicas mais rapidamente e facilmente em comparação com a álgebra booleana. Reduzir significa simplificar, reduzindo o número de portões e entradas. Gostamos de simplificar a lógica para uma forma de menor custo para economizar custos pela eliminação de componentes. Definimos o menor custo como sendo o menor número de portas com o menor número de entradas por porta. Com uma escolha, a maioria dos alunos faz a simplificação lógica com mapas de Karnaugh, em vez da álgebra booleana, uma vez que eles aprendem essa ferramenta.

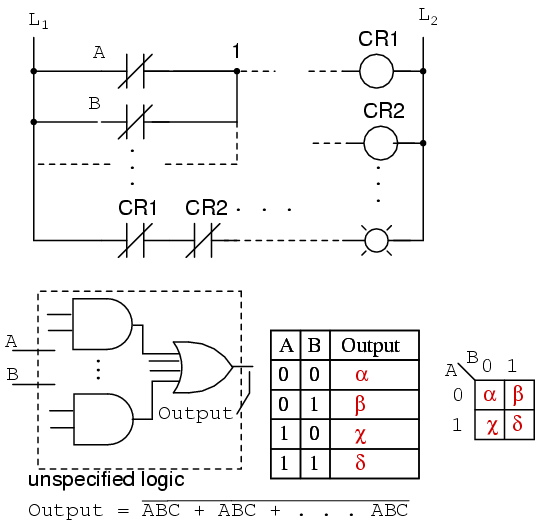

Mostramos cinco itens individuais acima, que são apenas maneiras diferentes de representar a mesma coisa: uma função lógica digital de 2 entradas arbitrária. A primeira é a lógica ladder de relé, depois portas lógicas, uma tabela de verdade, um mapa de Karnaugh e uma equação booleana. O ponto é que qualquer um deles é equivalente. Duas entradas A e B podem assumir valores de 0 ou 1 , alto ou baixo, aberto ou fechado, True ou False, conforme o caso. Existem 2 2 = 4 combinações de entradas produzindo uma saída.

✏️ Responder

Para escrever sua resposta aqui, entre ou crie uma conta.

Compartilhar